# Few-Layer Black Phosphorus Field-Effect Transistors with Reduced Current Fluctuation

Junhong Na,<sup>†</sup> Young Tack Lee,<sup>†</sup> Jung Ah Lim,<sup>†</sup> Do Kyung Hwang,<sup>†</sup> Gyu-Tae Kim,<sup>‡</sup> Won Kook Choi,<sup>\*,†</sup> and Yong-Won Song<sup>\*,†</sup>

<sup>†</sup>Interface Control Research Center, Future Convergence Research Division, Korea Institute of Science and Technology, Seoul 136-791, South Korea, and <sup>‡</sup>School of Electrical Engineering, Korea University, Seoul 136-713, South Korea

**ABSTRACT** We investigated the reduction of current fluctuations in few-layer black phosphorus (BP) field-effect transistors resulting from  $Al_2O_3$  passivation. In order to verify the effect of  $Al_2O_3$  passivation on device characteristics, measurements and analyses were conducted on thermally annealed devices before and after the passivation. More specifically, static and low-frequency noise analyses were used in monitoring the charge transport characteristics in the devices. The carrier number fluctuation (CNF) model, which is related to the charge trapping/detrapping process near the interface between the channel and gate dielectric, was employed to describe the current fluctuation phenomena. Noise reduction due to the  $Al_2O_3$  passivation was expressed in terms of the reduced interface trap density values  $D_{tt}$  and  $N_{ttr}$  extracted from the subthreshold slope (SS) and the CNF model, respectively. The

deviations between the interface trap density values extracted using the SS value and CNF model are elucidated in terms of the role of the Schottky barrier between the few-layer BP and metal contact. Furthermore, the preservation of the Al<sub>2</sub>O<sub>3</sub>-passivated few-layer BP flakes in ambient air for two months was confirmed by identical Raman spectra.

KEYWORDS: phosphorene · black phosphorus · low-frequency noise · Al<sub>2</sub>O<sub>3</sub> · passivation

remendous interest in two-dimensional van der Waals (vdW) layered materials such as graphene,<sup>1-3</sup>  $MoS_{2}$ , <sup>4-6</sup>  $WSe_{2}$ , <sup>7-9</sup> and other transitionmetal dichalcogenides (TMDs)<sup>10-13</sup> has been devoted to the field of electronic and optoelectronic applications. Because graphene suffers from the lack of a band gap, it exhibits a semimetallic property; thus, it is not suitable as a channel material in transistor and logic applications.<sup>14,15</sup> In 2011, monolayer MoS<sub>2</sub> field-effect transistors (FETs) were recorded to exhibit a high carrier mobility of  $\sim$ 217  $cm^2 V^{-1} s^{-1}$  and high on/off current ratio of  $\sim 10^8$  owing to the suppression of Coulomb scattering in a high-k environment and the existence of a reasonable band gap (~1.8 eV for monolayer and  $\sim$ 1.2 eV for multilayer MoS<sub>2</sub>), respectively.<sup>6</sup> This carrier mobility value was corrected later to  $\sim 15 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  by properly calculating the gate capacitance in a dual-gate configuration.<sup>16,17</sup> However, the mechanism of the high-k effect on vdW layered materials remains unclear; thus, relevant studies have to be continuously conducted.

Studies to enhance the carrier mobility values of MoS<sub>2</sub> transistors in terms of intrinsic or extrinsic treatment effects on MoS<sub>2</sub> are ongoing.<sup>4</sup> The literature on intrinsic treatments that alter the structural defects of MoS<sub>2</sub> such as point defects, dislocations, and so on is currently very few. Some research activities regarding the plasma treatment effects on MoS<sub>2</sub> were reported.<sup>18,19</sup> Further intensive works to obtain high-quality MoS<sub>2</sub> and other vdW layered materials have to be conducted. In contrast to the efforts in enhancing the intrinsic effects, extrinsic treatment approaches that improved the interface qualities between the MoS<sub>2</sub> and the metal electrodes or gate dielectrics are thoroughly studied. Alternative metals that form an interface with MoS<sub>2</sub> and are used as electrodes for devices were considered to decrease the effective Schottky barrier height and reduce the contact resistance, which is explained in terms of the work function variation and Fermi level energy pinning.<sup>5,20,21</sup> For example, scandium metalcontacted MoS<sub>2</sub> transistors recorded high

\* Address correspondence to wkchoi@kist.re.kr, ysong@kist.re.kr.

Received for review September 16, 2014 and accepted November 2, 2014.

Published online November 04, 2014 10.1021/nn5052376

JAI

www.acsnano.org

© 2014 American Chemical Society

VOL. 8 • NO. 11 • 11753-11762 • 2014

carrier mobility values of  $\sim 184 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1.5}$  Using external dopants such as potassium,<sup>22</sup> polyethylenimine (PEI),<sup>23</sup> and benzyl viologen (BV),<sup>24</sup> we can also realize an increase in the MoS<sub>2</sub> device performance. In addition, enhancement in the interface quality between MoS<sub>2</sub> and the gate dielectric can also be regarded as one of the extrinsic treatment approaches to increase the carrier mobility in transistors; therefore, various gate dielectrics such as poly(methyl methacrylate) (PMMA),<sup>25</sup> Al<sub>2</sub>O<sub>3</sub>,<sup>26</sup> and boron nitride<sup>27,28</sup> have been applied to the MoS<sub>2</sub> devices. In various dielectric environments, for example, MoS<sub>2</sub> transistors encapsulated and passivated with PMMA<sup>25</sup> and Al<sub>2</sub>O<sub>3</sub><sup>5</sup> showed high carrier mobility values such as  $\sim$ 470 and  $\sim$ 700 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature, respectively. Currently, however, these superior carrier mobility values of MoS<sub>2</sub> devices discussed above require continuing studies, whose results would show comparable results to ensure reliability.

In the absence of critical intrinsic or extrinsic treatment approaches, black phosphorus (BP), another vdW layered material, has been demonstrated as a channel material that can achieve high-performance FETs with a carrier mobility value of  $\sim 1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature, even in the form of few-layer BP transistors.<sup>29</sup> According to the results from another study that reported carrier mobility values on the order of  $10^2$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1,30,31</sup> BP materials can somewhat retain the bulk carrier mobility value in a few-layer form, in contrast to other TMDs. From this perspective, few-layer BPs are considered as a promising channel material for high-performance electronic device applications. To further increase the device performance and realize better device analysis on few-layer BP FETs, research on the effects of high-k layer on few-layer BPs must be profoundly pursued relative to other vdW layered materials.

The low-frequency noise (LFN) characterization method has been used as a tool for diagnosing carrier transport behavior and interface quality between a semiconductor and an insulator in conventional metal-oxide-semiconductor FETs (MOSFETs).<sup>32-34</sup> Other methods of obtaining interface guality information on the devices, namely, capacitance-voltage measurement and deep-level transient spectroscopy, are limited by the area size of the interface; hence, measurement using nanoscale devices becomes difficult.<sup>34</sup> Fortunately, LFN measurement can be applied regardless of the area size of the interface, which is one of the advantages of this method in nanodevice analysis. Because downscaling of the device can aggressively be performed, the increase in signal-to-noise ratio emphasizes the importance of LFN characterizations.<sup>33</sup> In addition, reduction in the noise level in the devices can affect the device performance; therefore noise-level reduction methods in vdW materials have to be developed and analyzed. To the best

of our knowledge, our work on the LFN characteristics of few-layer BP FETs is the first report on this subject. We also propose a method to reduce the current fluctuations using an  $Al_2O_3$ -passivation layer.

## **RESULTS AND DISCUSSION**

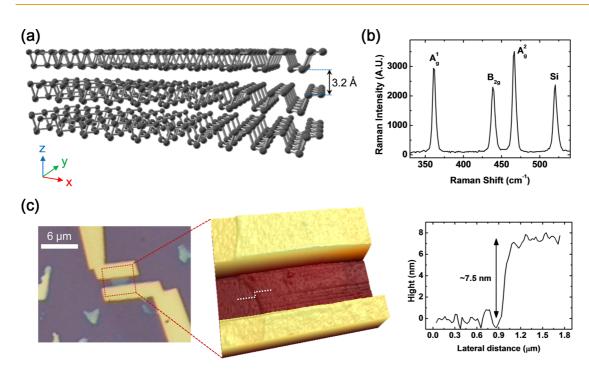

BP is one of the layered materials in which each layer is stacked with vdW interactions along the z-direction, as shown in Figure 1a.<sup>29,35</sup> The interlayer distance between the closest individual layers is estimated to be  $\sim$ 0.32 nm.<sup>36</sup> A few-layer BP can also be exfoliated from bulk BP and placed onto a Si/SiO<sub>2</sub> substrate, which consists of a highly p<sup>++</sup> Si and a thermally oxidized 300 nm thick SiO<sub>2</sub> layer in this study. Representative Raman spectra (532 nm, Nd:Yag laser) of a few-layer BP onto the Si/SiO<sub>2</sub> substrate are shown in Figure 1b, and the Raman peak locations  $(A_g^{-1} \sim 361 \text{ cm}^{-1}, B_{2g} \sim 439 \text{ cm}^{-1}, \text{ and } A_g^{-2} \sim 467 \text{ cm}^{-1})$ indicate that the material is a BP.<sup>30,31,35</sup> To characterize the electrical properties of few-layer BPs, an Au-only metal (~100 nm thick) was used as a source and drain electrode using subsequent electron beam lithography and thermal evaporation. The optical image of the as-fabricated few-layer BP device is shown in Figure 1c (left image). To determine the thickness of the fewlayer BP, atomic force microscopy (AFM) was used, and the three-dimensional image is shown in Figure 1c (center image). The thickness of the few-layer BP was confirmed to be  $\sim$ 7.5 nm, as shown in Figure 1c (right image). Thermal annealing and Al<sub>2</sub>O<sub>3</sub> deposition were sequentially applied to the devices, and static and LFN measurements were performed between process intervals.

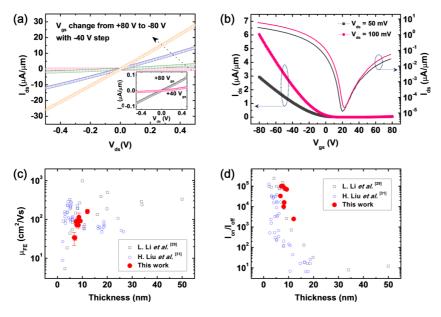

Figure 2a shows the typical output characteristics of a few-layer BP FET, which is identical to that shown in Figure 1c; this device has just been thermally annealed. The ohmic-like behavior at a high gate voltage such as  $V_{\rm qs} = -40$  and -80 V implies that the Schottky-barrierinduced series resistances can be ignored. The trend of the gate-voltage-dependent drain current result shown in the inset of Figure 2a is opposite of the data shown in Figure 2a. This behavior matches the transfer characteristics of the few-layer BP FET shown in Figure 2b. In the region of high positive gate voltages  $(V_{as} > 20 \text{ V})$ , the electron is the dominant charge carrier; thus, the drain current increases as the gate voltage positively increases. In the region of moderate negative gate voltages ( $V_{qs}$  < 20 V), the hole becomes the dominant charge carrier; thus, the device displays p-type behavior. Similar to that shown by the graph in Figure 2b, p-branch-enhanced ambipolar characteristics appear in most of the thermally annealed few-layer BP FETs. We note that the devices used in this study are thermally annealed unless otherwise specified. Additionally, field-effect mobility ( $\mu_{FE}$ ) values in this study are calculated from transfer characteristics such as in Figure 2b by using  $\mu_{FE} = L/(WC_{ox}V_{ds})g_{m}$ , where W and

VOL. 8 • NO. 11 • 11753-11762 • 2014

JAI

www.acsnano.org

Figure 1. (a) Schematic image of a few-layer BP. (b) Raman spectrum of a few-layer BP placed on a SiO<sub>2</sub>/Si substrate measured at room temperature and ambient air. (c) (Left) Optical image of a source/drain metal-contacted few-layer BP. (Center) Threedimensional image of a few-layer BP with Au contact metals measured by AFM. (Right) Thickness of the few-layer BP was measured to be  $\sim$ 7.5 nm.

Figure 2. (a) Output characteristics of the few-layer BP FET as a function of the gate voltage. This device is the same as that shown in Figure 1c. The inset shows the same output characteristics but exhibits only those of gate voltages +80 and +40 V. The channel length and width of this device are  $\sim$ 1.1 and  $\sim$ 2.6  $\mu$ m, respectively. (b) Corresponding transfer characteristics of the few-layer BP FET at  $V_{ds} = 50$  mV and  $V_{ds} = 100$  mV. (c) Field-effect mobility  $\mu_{FE}$  and (d) on/off current ratio  $I_{on}/I_{off}$  data set of this study as a function of the thickness of a few-layer BP together with the digitized data from other literature.<sup>29,31</sup> The error bars in the  $\mu_{FE}$  values are associated with various drain voltages and double-swept data in the transfer characteristics.

L are the length and width of the channel, respectively;  $C_{\rm ox}$  is the gate capacitance per unit area; and  $g_{\rm m}$  is the transconductance.

The thickness-dependent  $\mu_{FE}$  and on/off current ratio of our few-layer BP FETs are shown in Figures 2c and d, respectively, along with the earlier reported data by Li et al.<sup>29</sup> and Liu et al.<sup>31</sup> The obtained results match

well with the trend of the reported data. As the thickness increases within the range in our results,  $\mu_{\rm FE}$  also increases because the charge impurity scattering at the interface can be more effectively reduced in thicker samples due to the screening effect resulting from the accumulated charge carrier layer in the fewlayer BP channel.<sup>29,37</sup> In contrast, the on/off current

VOL.8 • NO.11 • 11753-11762 • 2014

IAI www.acsnano.org

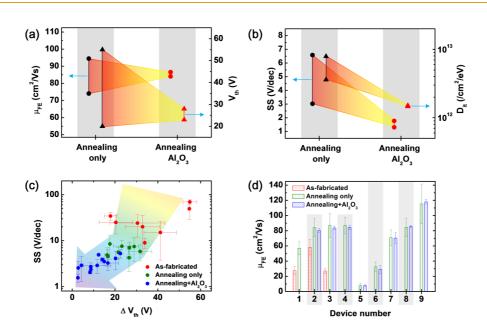

Figure 3. Static analysis and quantitative data of the few-layer BP FETs in relation to the thermal annealing and  $AI_2O_3$ passivation effect. (a and b)  $\mu_{FE}$ ,  $V_{th}$ , SS, and  $D_{it}$  changes of the few-layer BP FET before and after  $AI_2O_3$  passivation, denoted by "Annealing only" and "Annealing  $AI_2O_3$ ". This device is the same as that shown in Figure 2a and b. The two different values in each case result from the double gate voltage swept data. (c) Quantitative SS and  $\Delta V_{th}$  data for three cases of few-layer BP FETs: "As-fabricated", "Annealing only", and "Annealing +  $AI_2O_3$ ". The  $\Delta V_{th}$  values are the  $V_{th}$  difference between the double gate voltage swept data. The gradated arrow is provided for visual guidance. (d)  $\mu_{FE}$  changes in three steps for each few-layer BP FET.

ratio decreases when the thickness increases, as shown in Figure 2d, which probably results from the increase in the number of independent layers in the gate voltage; that is, the charge carriers in these layers cannot be depleted using the back gate voltage.<sup>29</sup> When the thickness increases, the increase in the interlayer resistance reduces  $\mu_{FE}$ , as described in studies related to  $MoS_2$ , due to the top-contacted geometry of the devices.<sup>37,38</sup> However, the interlayer resistance value of the BP is likely to be relatively smaller than that of MoS<sub>2</sub>. Therefore, significant reduction in  $\mu_{\text{FF}}$  is not observed,<sup>29,37</sup> which can also be considered as an advantage in terms of device operation. For logic device applications, therefore, the rational thickness of the BP layer can be  $\sim$ 8 nm, together with high  $\mu_{\rm FE}$  and on/off current ratio.

The  $\mu_{\rm FF}$  values shown in Figure 2c are an order of magnitude lower than the bulk mobility values for the hole  $\sim 1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature,<sup>35</sup> which could be attributed to several factors. First, the series resistance portion, which can be induced by the BP-metal contact interface and interlayer resistance, is one of the causes for the decrease in the extrinsic mobility.<sup>5,37,38</sup> Remnant molecules on the BP surface, such as oxygen and water, can be applied to the charge traps and/or scattering centers.<sup>39,40</sup> The imperfect interface between the BP and SiO<sub>2</sub> may also reduce carrier mobility.<sup>28,41</sup> Anisotropic conductivity in the x and y directions (in-plane; see Figure 1a) can be an obstacle in achieving the highest mobility if the electrodes are randomly fabricated regardless of the crystal direction.<sup>35,42</sup> In addition, structural defects and

NA ET AL.

surface oxidation in the BP layer can act as scattering sites and reduce carrier mobility.<sup>42</sup> Recently, according to the calculation of Qiao *et al.*,<sup>36</sup> the phonon-limited hole mobility of a few-layer BP device with five layers can reach ~5000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature. Few-layer BP devices can be more attractively applied as channel materials for FETs than any other vdW layered materials once the above-mentioned causes for the decrease in the mobility of few-layer BPs are solved using controlled methods such as appropriate high-*k* gate dielectric environment, passivation, metal electrodes, and so on.

To determine the Al<sub>2</sub>O<sub>3</sub>-passivation effect on fewlayer BP FETs, additional static device parameters such as  $\mu_{FE}$ , hysteresis, subthreshold slope (SS), and interface trap density ( $D_{it}$ ) must be known. These quantitative data should also be extracted before and after the Al<sub>2</sub>O<sub>3</sub> deposition, which are denoted as "Annealing only" and "Annealing Al<sub>2</sub>O<sub>3</sub>," respectively, in Figure 3. We note that hysteresis is defined as the threshold voltage difference ( $\Delta V_{th}$ ) between the transfer curves swept toward the positive and negative directions, as shown in the right axis in Figure 3a. The typical hysteretic behavior in each step in the transfer characteristics of the few-layer BP FETs is shown in Figure S1 (Supporting Information). In addition,  $D_{it}$  is normally extracted from the SS using the following relationship:<sup>43</sup>

$$SS = \frac{k_{\rm B}T}{q} \ln 10 \left( \frac{C_{\rm ox} + C_{\rm s} + C_{\rm it}}{C_{\rm ox}} \right) \tag{1}$$

where *q* is the electronic charge;  $k_{\rm B}$  is the Boltzmann constant; *T* is the temperature in kelvin; and  $C_{\rm ox}$ ,  $C_{\rm s}$ , and

JAI

www.acsnano.org

$C_{it}$  are the gate, semiconductor, and interface-trap capacitances, respectively.  $C_{it}$  is equal to  $qD_{it}$ . The  $C_s$  can also be negligible due to the relatively thin BP layer.

The large variation among the  $\mu_{\rm FE}$  values for the annealed-only case compared with that for the Al<sub>2</sub>O<sub>3</sub>passivated case is attributed to the difference between the hysteresis values in each case, as shown in Figure 3a.<sup>42</sup> Obviously, hysteresis also causes variations in the other device parameters such as SS and  $D_{it}$ , as shown in Figure 3b. After the Al<sub>2</sub>O<sub>3</sub> passivation, the hysteresis is remarkably reduced from  $\sim$ 35 to  $\sim$ 5 V, as shown in Figure 3a, and the variations in the other parameters are accordingly reduced. Moreover, the mean values of the SS and D<sub>it</sub> shown in Figure 3b are reduced from  $\sim$ 4.8 to  $\sim$ 1.5 V dec $^{-1}$  and from  $\sim$ 5.7  $\times$  $10^{12}$  to  $\sim 1.5 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, respectively. Figure 3c shows that the quantitative changes in the SS and hysteresis values resulting from the thermal annealing and Al<sub>2</sub>O<sub>3</sub>-passivation effects on the device performance of the few-layer BP FETs are reliable. Asfabricated devices, i.e., devices before the thermal annealing process, have high SS and hysteresis values. After the thermal annealing, the SS values are significantly reduced, but the hysteresis values are only slightly reduced. The removal of polymer residues near the BP layers<sup>44–46</sup> and the improvement in the contact properties<sup>47,48</sup> through thermal annealing can affect the reduction in the SS values. In addition, the significantly improved  $\mu_{FE}$  values after thermal annealing shown in Figure 3d can also be attributed to these reasons.44-48 Thermal annealing and electrical measurement under vacuum are not the in situ processes applied in this study; thus, the hysteresis values can remain if the dominant hysteresis sources are adsorbates such as water and/or oxygen molecules near the BP layers and/or the silanol groups on the SiO<sub>2</sub> surface.<sup>39,49-52</sup> Through Al<sub>2</sub>O<sub>3</sub> passivation by the atomic layer deposition (ALD) process, the SS and hysteresis values are evidently reduced. The remaining water and/or oxygen molecules near the BP layers can be effectively removed during the preheating step of the ALD process ( $\sim$ 220 °C).<sup>49–51</sup> Further, the sequential chemisorptions of the trimethylaluminum (TMA) precursor to the hydroxyl groups on the SiO<sub>2</sub> and the surface oxidation layer of the BP can also reduce the water and/or oxygen molecules and hydroxyl groups that probably affect the SS and hysteresis values.<sup>53–55</sup> Afterward, the 30 nm thick Al<sub>2</sub>O<sub>3</sub> layer can also positively suppress the surface reactions between the BP layer and gas molecules during the device operation.<sup>53–55</sup> This tendency of reduced SS and hysteresis values by the Al<sub>2</sub>O<sub>3</sub> deposition suggests that the Al<sub>2</sub>O<sub>3</sub> passivation can be a positive method of realizing highperformance few-layer BP FETs. On one hand, the mean  $\mu_{\rm FE}$  values both before and after the Al<sub>2</sub>O<sub>3</sub> passivation (Figure 3a) are almost the same. Moreover, the  $\mu_{\rm FE}$  values extracted from each step for each device

remain the same after the Al<sub>2</sub>O<sub>3</sub> passivation, as shown in Figure 3d. Recently, a study has reported that the fixed oxide charges in an Al<sub>2</sub>O<sub>3</sub> layer can induce energy-band bending near the contact and modulate the type of operation in few-layer BP devices.<sup>56</sup> However, these devices had to suffer a decrease in the conductance and  $\mu_{\rm FE}$  values resulting from a large contact resistance.<sup>56</sup> On the other hand, the ALD Al<sub>2</sub>O<sub>3</sub> layer on the few-layer BP in our study did not randomly change the type of operation of the device but improved the device performance in terms of the SS and hysteresis, whereas the  $\mu_{\text{FE}}$  values remained stable, which implies that the role of the fixed oxide charges is insignificant. The unchanged  $\mu_{FE}$  values after the Al<sub>2</sub>O<sub>3</sub> passivation could have originated from the balanced competition of positive and negative factors: reduced adsorbates and/or hydroxyl groups during the ALD process, 53-55 suppression of Coulomb scattering due to the high-k screening effect, 5,6,17,26 high density of the fixed oxide charges in high-k dielectrics,<sup>56,57</sup> and remote phonon scattering of high-k dielectrics.<sup>58</sup> In fact, the effects of Al<sub>2</sub>O<sub>3</sub> deposition on the devices depend on the ALD process conditions,55,59 but we believe that this change trend in the device parameters as a result of the Al<sub>2</sub>O<sub>3</sub> passivation is more reliable because the effects of the thermal annealing process are also considered.

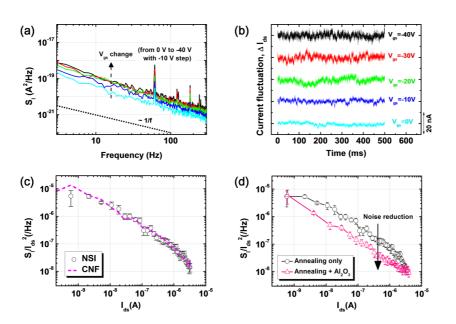

Figure 4a shows the drain current spectral density  $(S_l)$  as a function of the frequency at different gate voltages obtained from the LFN measurement of the thermally annealed few-layer BP FET, which is the same as that shown in Figure 3a and b. These data were Fourier transformed to the frequency range on the basis of the time-domain drain current fluctuation of the device at different gate voltages, as shown in Figure 4b. The degree of drain current fluctuations appears to increase as the gate voltage negatively increases, and clear expression of the phenomena can be easily seen in Figure 4a. Correspondingly,  $S_1$ (which is normally considered as a device noise level) also increases as the gate voltage negatively increases (Figure 4a), which results in the increase in the drain current. This is a typical tendency of the LFN characteristics in devices because the more charge carriers are produced, the more charge carriers are correlated to the noise sources.

Two types of LFN models are widely accepted to well describe the noise characteristics in conventional silicon MOSFETs: carrier number fluctuation (CNF) and Hooge mobility fluctuation (HMF) models.<sup>32,34</sup> The CNF model suggests that current fluctuations arise from the change in the charge carrier density due to the charge trapping/detrapping phenomena at the trap sites near the channel—insulator interface. The HMF model describes that the change in the carrier mobility resulting from the variation of the scattering cross section induced current fluctuations. To figure out which type

VOL.8 • NO.11 • 11753-11762 • 2014

Figure 4. LFN characteristics of the few-layer BP FET, which is the same device as that shown in Figure 3a and b. (a) Drain current spectral density as a function of frequency at various gate voltages for the thermally annealed few-layer BP FET. (b) Current fluctuation in the time domain at the same gate voltage values as those in (a). (c) Mean normalized drain current spectral density (NSI) as a function of the drain current at frequencies of 8, 9, 10, 11, and 12 Hz. The corresponding CNF model is fitted to the NSI data. (d) Noise reduction due to  $Al_2O_3$  passivation represented by the mean normalized drain spectral density as a function of the drain current before and after the  $Al_2O_3$  passivation.

of LFN model is dominant and well expresses the carrier transport behavior in a few-layer BP FET, the normalized drain current spectral density  $(S_{\rm f}/l_{\rm ds}{}^2)$  as a function of the drain current is shown in Figure 4c. In the CNF model, the normalized drain current spectral density can be expressed as<sup>32</sup>

$$\frac{S_l}{{I_{ds}}^2} = \left(\frac{g_m}{{I_{ds}}}\right)^2 S_{Vfb}$$

(2)

where  $g_{\rm m}$  is the gate transconductance and  $S_{\rm Vfb}$  is the flat band voltage spectral density, which can also be expressed as

$$S_{\rm Vfb} = \frac{q^2 k_{\rm B} T N_{\rm it}}{W L C_{\rm ox}^2 f}$$

(3)

where W and L are the width and length of the channel, respectively, and  $N_{\rm it}$  is the interface trap density. Using this CNF model, we obtain the best-fit result for the thermally annealed few-layer BP FET, as shown in Figure 4c. The thicker BP devices have lower on/off current ratio, as shown in Figure 2d; therefore, determining which type of noise model is appropriate for these devices is difficult. Different points of view may arise; however, this uncertainty is similar to the issue on why graphene FET is controversial in terms of deciding which dominant noise model is appropriate for it.<sup>2</sup> To further confirm the appropriate noise model for the few-layer BP device, we plot the equivalent input gate voltage spectral density  $(S_{Vq})$  as a function of the gate voltage in Figure S2. The flat region in the accumulation regime of the FET implies that the CNF model is the

appropriate noise model for the thermally annealed few-layer BP FETs because the other noise models, including the HMF and the carrier number fluctuation with correlated mobility fluctuation (CNF–CMF), are dependent on the gate voltage, presented in the Supporting Information.<sup>32,60,61</sup>

After the Al<sub>2</sub>O<sub>3</sub> passivation on the thermally annealed few-layer BP FETs, S<sub>I</sub>/I<sub>ds</sub>, which is also considered as a noise level, is reduced over the entire device operation regime, as shown in Figure 4d. This result implies that the trap sites that activate the charge fluctuations are reduced by the Al<sub>2</sub>O<sub>3</sub> passivation. According to the reduced SS and hysteresis values shown in Figure 3, we expect that the removal of the remaining adsorbates and hydroxyl group near the BP layer can affect the reduction in the noise level resulting from the suppression of the charge trapping/ detrapping process. More studies regarding the specific relationship between the Al<sub>2</sub>O<sub>3</sub> layer and few-layer BP FETs must be conducted; however, we should note that Al<sub>2</sub>O<sub>3</sub> passivation is one way of reducing the noise level in few-layer BP FETs.

To further analyze the LFN characteristics of the  $Al_2O_3$ -passivated few-layer BP FET, the  $S_l/l_{ds}^2$  data as a function of the drain current and the corresponding LFN models are shown in Figure S3. The CNF model does not fit in the hole accumulation regime, *i.e.*, the high positive gate voltage region. Therefore, the CNF–CMF model is introduced, which finally fits the  $S_l/l_{ds}^2$  data all over the region, indicating that the charge trapping/detrapping process in the trap sites can change the scattering rate, resulting in the

VOL.8 • NO.11 • 11753-11762 • 2014

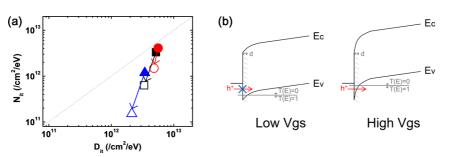

Figure 5. (a) Interface trap density values obtained from the LFN ( $N_{it}$ ) and transfer ( $D_{it}$ ) characteristics and changes (filled) before and (empty) after the Al<sub>2</sub>O<sub>3</sub> passivation. (b) Energy band diagrams near the metal-BP contact representing the tunneling probability T(E) for two regimes at low and high gate voltages.

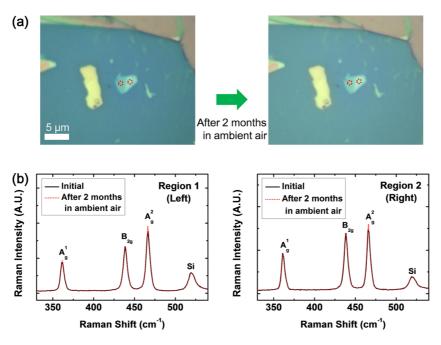

Figure 6.  $Al_2O_3$ -passivation effect on the Raman spectra of the few-layer BP. (a) Optical images of (right) the few-layer BP flakes passivated with  $Al_2O_3$  layer and (left) the same flakes stored in ambient air after two months. (b) Raman spectra corresponding to the same few-layer BP flakes indicated by the two red and dashed circles (left and right) in (a).

fluctuation of the charge carrier mobility.<sup>32–34</sup> From both the CNF and CNF–CMF models, the interface trap density  $N_{it}$  can be extracted using eq 3. By dealing with the device shown in Figure 4, the  $N_{it}$  values for the thermally annealed and Al<sub>2</sub>O<sub>3</sub>-passivated few-layer BP FETs are obtained as ~1.2 × 10<sup>12</sup> and ~1.5 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>, respectively. These values are within the range from 10<sup>9</sup> to 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> for the Si–SiO<sub>2</sub> and Si–high-*k* interface, respectively.<sup>34</sup>

Figure 5a shows the change in the  $D_{it}$  and  $N_{it}$  values extracted using the static and LFN analyses corresponding to eqs 1 and 3 for three different few-layer BP FETs before and after the  $Al_2O_3$  passivation. It is noted that the  $D_{it}$  and  $N_{it}$  values were assumed to be independent of energy.<sup>62,63</sup> Both the  $D_{it}$  and  $N_{it}$  values are reduced after the  $Al_2O_3$ -passivation process, which is the same effect as that on the device parameters and noise level of the few-layer BP FETs discussed earlier. The  $D_{it}$  and  $N_{it}$  values are different from each other for each identical device, which can be ascribed to the following factors: first, the  $D_{it}$  value is calculated from the SS, which might be less accurate because the deep subthreshold region can be hidden in the case of an unclear off-current region. Thus, the SS values may be imprecise in this case. In the three devices in Figure 5a, however, the on/off current ratio values are over  $10^4$ ; thus, the SS deviations can be minimized. More importantly, the SS equation can be changed in Schottky barrier FETs:<sup>64</sup>

$$SS = \frac{k_{\rm B}T}{q} \ln 10 \left(\frac{1}{2} + \frac{\lambda}{d}\right) \tag{4}$$

where  $\lambda$  is the screening length defined as  $(\varepsilon_r \varepsilon_{ox}^{-1} t_r t_{ox})^{1/2}$ (in which  $\varepsilon_r$  and  $\varepsilon_{ox}$  are the BP and SiO<sub>2</sub> dielectric constants and  $t_r$  and  $t_{ox}$  are the BP and SiO<sub>2</sub> thicknesses, respectively) and *d* is the tunneling distance. The tunneling probability is zero if the width of the Schottky barrier is larger than *d*. Assuming that *d* is constant, the SS value depends on the BP and SiO<sub>2</sub> thicknesses, as expressed in eq 4. Thus, the SS value ARTICL

VOL.8 • NO.11 • 11753-11762 • 2014

cannot provide information regarding the interface trap density in this case. However, the kinked point in the transfer curve of the Schottky barrier FET, which represents the change of the carrier transport mechanism at the contact,<sup>64,65</sup> is not observed in our devices. Therefore, the Schottky barrier is insignificant in our devices but can still affect the SS values. It is worth noting that the SS value is extracted in the subthreshold region, which is in the low gate voltage regime; thus, the width of the Schottky barrier can be large, resulting in imprecise D<sub>it</sub> values, as shown by the energy band diagrams in Figure 5b. On the other hand, the  $N_{\rm it}$  values obtained from the LFN analysis may more precisely reflect the interface trap density information because CNF model fitting is performed on the entire device operation regime, including the high gate voltage region, as shown in Figure 4c. Therefore, analyzing the LFN characteristics of the few-layer BP FETs is needed to obtain accurate interface quality information and understand the charge carrier transport properties.

BP flakes are well known to degrade when stored in ambient air without any passivation layers.<sup>29,30,66</sup> This phenomenon has not been precisely investigated yet, but surface reactions with gas molecules in ambient air have been considered as a dominant factor in the degradation. To further verify the ALD  $Al_2O_3$ -passivation effect, the few-layer BP flakes passivated with an  $Al_2O_3$ layer were stored in ambient air at room temperature for two months. The optical images and Raman spectra shown in Figure 6 confirm that the  $Al_2O_3$  layer can effectively block the surface reactions between the BP and gas molecules in ambient air, resulting in the passivation effect on the few-layer BP flakes. This result suggests that the ALD  $Al_2O_3$  layer can be a promising candidate in passivating few-layer BP flakes and enhancing the device performance.

## CONCLUSION

In summary, current fluctuation, also considered as a noise level in devices, was reduced all over the device operation regime in few-layer BP FETs as a result of Al<sub>2</sub>O<sub>3</sub> passivation. Our static analysis also confirmed the positive effects of the Al<sub>2</sub>O<sub>3</sub> passivation on the devices by qualitatively and quantitatively monitoring the device parameters such as the hysteresis, SS, and  $D_{\rm it}$ . Moreover, through a separate analysis of the thermal annealing and Al<sub>2</sub>O<sub>3</sub>-passivation effects, the static and LFN characteristics of few-layer BP FETs were verified to be more reliable. To analyze the LFN characteristics, we introduced the CNF model that suggests that current fluctuation is induced by the charge carrier trapping/detrapping process in the trap sites near the gate insulator. By comparing the  $D_{it}$  and  $N_{it}$  values obtained from the static and LFN analyses, respectively, we observed the same trend in which the interface trap density values decreased after the Al<sub>2</sub>O<sub>3</sub> passivation. The deviation between these values was explained to be due to the Schottky barrier contact between the metal and few-layer BP flake. Finally, we confirmed through the identical Raman spectra that the Al<sub>2</sub>O<sub>3</sub> passivation plays a major role in conserving the few-layer BP flakes in ambient air for two months. Our study can be applied in understanding the role of high-k dielectric in the performance of the few-layer BP FETs and in realizing high-performance passivated few-layer BP FETs.

#### **EXPERIMENTAL METHODS**

**Thermal Annealing.** First, the as-fabricated BP devices were placed onto the center of a horizontal tube furnace (Lindberg Blue from Thermo Scientific), and the chamber was depressurized to a low-vacuum level of  $\sim 7 \times 10^{-2}$  Torr. This vacuum level was maintained during the entire thermal annealing process. The temperature in the chamber was sequentially increased up to 220 °C for 15 min and maintained for 5 h in the absence of any gas flows. Thereafter, the temperature was gradually decreased to room temperature.

$\rm Al_20_3$  Deposition. By applying the ALD process (Atomic Classic, CN-1 Corporation), a 30 nm thick  $\rm Al_2O_3$  layer was deposited on the BP devices at 220 °C for an 8 h growth duration (235 cycles at a growth rate of 1.3 Å cycle^{-1}). The aluminum and oxygen precursors were TMA (UP Chemical Co., Ltd.) and deionized water, respectively. For the carrier and purging gas, ultrapure N\_2 (99.999%) was used at a rate of 200 sccm. The ALD cycle followed the sequence H\_2O (1 s)/N\_2 (60 s)/TMA (1 s)/N\_2 (60 s). The initial vacuum level of the growth chamber was  $\sim 5 \times 10^{-2}$  Torr and maintained at  $\sim 1$  Torr during the deposition.

**Electrical Characterization.** All static and ac measurements were carried out in room temperature and high vacuum ( $\sim 5 \times 10^{-5}$  Torr) using a cryogenic probe station (CPX-VF, Lakeshore). The static electrical properties of the FETs were measured using a HP 4155C semiconductor parameter analyzer. LFN measurements were performed using our custom LFN characterization system,<sup>67</sup> which was configured using a data acquisition module.

Conflict of Interest: The authors declare no competing financial interest.

Supporting Information Available: The hysteretic behaviors of transfer characteristics and further LFN analyses in few-layer BP FETs are described in detail here. This material is available free of charge *via* the Internet at http://pubs.acs.org.

*Acknowledgment.* This work was supported by the Korea Institute of Science and Technology (KIST) Future Resource Research Program (2E24871).

### **REFERENCES AND NOTES**

- Geim, A. K.; Novoselov, K. S. The Rise of Graphene. Nat. Mater. 2007, 6, 183–191.

- Balandin, A. A. Low-Frequency 1/f Noise in Graphene Devices. Nat. Nanotechnol. 2013, 8, 549–555.

- Yang, H.; Heo, J.; Park, S.; Song, H. J.; Seo, D. H.; Byun, K.-E.; Kim, P.; Yoo, I.; Chung, H.-J.; Kim, K. Graphene Barristor, a Triode Device with a Gate-Controlled Schottky Barrier. *Science* 2012, 336, 1140–1143.

- Jung, Y.; Shen, J.; Cha, J. Surface Effects on Electronic Transport of 2D Chalcogenide Thin Films and Nanostructures. *Nano Convergence* 2014, 1, 18–28.

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2012**, *13*, 100–105.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Huang, J.-K.; Pu, J.; Hsu, C.-L.; Chiu, M.-H.; Juang, Z.-Y.; Chang, Y.-H.; Chang, W.-H.; Iwasa, Y.; Takenobu, T.; Li, L.-J. Large-Area Synthesis of Highly Crystalline WSe<sub>2</sub> Monolayers and Device Applications. ACS Nano **2013**, 8, 923–930.

- Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- 9. Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Optoelectronic Devices Based on Electrically Tunable p-n Diodes in a Monolayer Dichalcogenide. *Nat. Nanotechnol.* **2014**, *9*, 262–267.

- Chamlagain, B.; Li, Q.; Ghimire, N. J.; Chuang, H.-J.; Perera, M. M.; Tu, H.; Xu, Y.; Pan, M.; Xaio, D.; Yan, J.; *et al.* Mobility Improvement and Temperature Dependence in MoSe<sub>2</sub> Field-Effect Transistors on Parylene-C Substrate. *ACS Nano* 2014, *8*, 5079–5088.

- Perea-López, N.; Elías, A. L.; Berkdemir, A.; Castro-Beltran, A.; Gutiérrez, H. R.; Feng, S.; Lv, R.; Hayashi, T.; López-Urías, F.; Ghosh, S.; et al. Photosensor Device Based on Few-Layered WS<sub>2</sub> Films. Adv. Funct. Mater. 2013, 23, 5511–5517.

- Lin, Y.-F.; Xu, Y.; Wang, S.-T.; Li, S.-L.; Yamamoto, M.; Aparecido-Ferreira, A.; Li, W.; Sun, H.; Nakaharai, S.; Jian, W.-B.; *et al.* Ambipolar MoTe<sub>2</sub> Transistors and Their Applications in Logic Circuits. *Adv. Mater.* **2014**, *26*, 3263–3269.

- Chhowalla, M.; Shin, H. S.; Eda, G.; Li, L.-J.; Loh, K. P.; Zhang, H. The Chemistry of Two-Dimensional Layered Transition Metal Dichalcogenide Nanosheets. *Nat. Chem.* **2013**, *5*, 263–275.

- 14. Editorial. Graphene Is Not Alone. *Nat. Nanotechnol.* **2012**, 7, 683–683.

- 15. Schwierz, F. Graphene Transistors: Status, Prospects, and Problems. *Proc. IEEE* **2013**, *101*, 1567–1584.

- Fuhrer, M. S.; Hone, J. Measurement of Mobility in Dual-Gated MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2013, 8, 146–147.

- Radisavljevic, B.; Kis, A. Reply to 'Measurement of Mobility in Dual-Gated MoS<sub>2</sub> Transistors'. *Nat. Nanotechnol.* 2013, 8, 147–148.

- Chen, M.; Nam, H.; Wi, S.; Priessnitz, G.; Gunawan, I. M.; Liang, X. Multibit Data Storage States Formed in Plasma-Treated MoS<sub>2</sub> Transistors. ACS Nano 2014, 8, 4023–4032.

- Chen, M.; Nam, H.; Wi, S.; Ji, L.; Ren, X.; Bian, L.; Lu, S.; Liang, X. Stable Few-Layer MoS<sub>2</sub> Rectifying Diodes Formed by Plasma-Assisted Doping. *Appl. Phys. Lett.* **2013**, *103*, 142110–4.

- Chuang, S.; Battaglia, C.; Azcatl, A.; McDonnell, S.; Kang, J. S.; Yin, X.; Tosun, M.; Kapadia, R.; Fang, H.; Wallace, R. M.; *et al.* MoS<sub>2</sub> P-Type Transistors and Diodes Enabled by High Work Function MoO<sub>x</sub> Contacts. *Nano Lett.* **2014**, *14*, 1337–1342.

- Gong, C.; Colombo, L.; Wallace, R. M.; Cho, K. The Unusual Mechanism of Partial Fermi Level Pinning at Metal–MoS<sub>2</sub> Interfaces. *Nano Lett.* **2014**, *14*, 1714–1720.

- Fang, H.; Tosun, M.; Seol, G.; Chang, T. C.; Takei, K.; Guo, J.; Javey, A. Degenerate n-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. *Nano Lett.* **2013**, *13*, 1991–1995.

- Yuchen, D.; Han, L.; Neal, A. T.; Mengwei, S.; Ye, P. D. Molecular Doping of Multilayer MoS<sub>2</sub> Field-Effect Transistors: Reduction in Sheet and Contact Resistances. *IEEE Electron Device Lett.* **2013**, *34*, 1328–1330.

- 24. Kiriya, D.; Tosun, M.; Zhao, P.; Kang, J. S.; Javey, A. Air-Stable Surface Charge Transfer Doping of MoS<sub>2</sub> by Benzyl Viologen. J. Am. Chem. Soc. **2014**, *136*, 7853–7856.

- Bao, W.; Cai, X.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High Mobility Ambipolar MoS<sub>2</sub> Field-Effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* **2013**, *102*, 042104–4.

- Kim, S.; Konar, A.; Hwang, W. S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J. B.; Choi, J. Y.; *et al*. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. *Nat. Commun.* **2012**, *3*, 1011–1017.

- Lee, G.-H.; Yu, Y.-J.; Cui, X.; Petrone, N.; Lee, C.-H.; Choi, M. S.; Lee, D.-Y.; Lee, C.; Yoo, W. J.; Watanabe, K.; *et al.* Flexible and Transparent MoS<sub>2</sub> Field-Effect Transistors on Hexagonal Boron Nitride-Graphene Heterostructures. *ACS Nano* 2013, 7, 7931–7936.

- Chan, M. Y.; Komatsu, K.; Li, S.; Xu, Y.; Darmawan, P.; Kuramochi, H.; Shu, N.; Ferreira, A. A.; Watanabe, K.; Taniguchi, T.; et al. Suppressed Thermally Activated Carrier Transport in Atomically Thin MoS<sub>2</sub> on Crystalline Hexagonal Boron Nitride Substrates. Nanoscale **2013**, *5*, 9572–9576.

- Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black Phosphorus Field-Effect Transistors. *Nat. Nanotechnol.* **2014**, *9*, 372–377.

- Koenig, S. P.; Doganov, R. a.; Schmidt, H.; Castro Neto, A. H.; Özyilmaz, B. Electric Field Effect in Ultrathin Black Phosphorus. *Appl. Phys. Lett.* **2014**, *104*, 103106–4.

- Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tománek, D.; Ye, P. D. Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility. ACS Nano 2014, 8, 4033–4041.

- Ghibaudo, G.; Roux, O.; Nguyen-Duc, C.; Balestra, F.; Brini, J. Improved Analysis of Low Frequency Noise in Field-Effect MOS Transistors. *Phys. Status Solidi A* **1991**, *124*, 571–581.

- 33. Ghibaudo, G.; Boutchacha, T. Electrical Noise and RTS Fluctuations in Advanced CMOS Devices. *Microelectron. Reliab.* **2002**, *42*, 573–582.

- 34. von Haartman, M.; Östling, M. Low-Frequency Noise in Advanced MOS Devices; Springer: Berlin, 2007.

- 35. Morita, A. Semiconducting Black Phosphorus. *Appl. Phys.* A: Mater. Sci. Process. **1986**, 39, 227–242.

- Qiao, J.; Kong, X.; Hu, Z.-X.; Yang, F.; Ji, W. High-Mobility Transport Anisotropy and Linear Dichroism in Few-Layer Black Phosphorus. *Nat. Commun.* 2014, *5*, 4475.

- Das, S.; Appenzeller, J. Screening and Interlayer Coupling in Multilayer MoS<sub>2</sub>. *Phys. Status Solidi RRL* 2013, *7*, 268–273.

- Na, J.; Shin, M.; Joo, M.-K.; Huh, J.; Jeong Kim, Y.; Jong Choi, H.; Hyung Shim, J.; Kim, G.-T. Separation of Interlayer Resistance in Multilayer MoS<sub>2</sub> Field-Effect Transistors. *Appl. Phys. Lett.* **2014**, *104*, 233502–5.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

- Park, W.; Park, J.; Jang, J.; Lee, H.; Jeong, H.; Cho, K.; Hong, S.; Lee, T. Oxygen Environmental and Passivation Effects on Molybdenum Disulfide Field Effect Transistors. *Nanotechnology* **2013**, *24*, 095202–5.

- Li, Y.; Xu, C.-Y.; Hu, P.; Zhen, L. Carrier Control of MoS<sub>2</sub> Nanoflakes by Functional Self-Assembled Monolayers. ACS Nano 2013, 7, 7795–7804.

- Hong, T.; Chamlagain, B.; Lin, W.; Chuang, H.-J.; Pan, M.; zhou, z.; Xu, Y. Polarized Photocurrent Response in Black Phosphorus Field-Effect Transistors. *Nanoscale* **2014**, *6*, 8978–8983.

- 43. Sze, S. M.; Ng, K. K. *Physics of Semiconductor Devices*; Wiley: New York, 2006.

- Chan, J.; Venugopal, A.; Pirkle, A.; McDonnell, S.; Hinojos, D.; Magnuson, C. W.; Ruoff, R. S.; Colombo, L.; Wallace, R. M.; Vogel, E. M. Reducing Extrinsic Performance-Limiting Factors in Graphene Grown by Chemical Vapor Deposition. *ACS Nano* 2012, *6*, 3224–3229.

- Cheng, Z.; Zhou, Q.; Wang, C.; Li, Q.; Wang, C.; Fang, Y. Toward Intrinsic Graphene Surfaces: A Systematic Study on Thermal Annealing and Wet-Chemical Treatment of SiO<sub>2</sub>-Supported Graphene Devices. *Nano Lett.* **2011**, *11*, 767–771.

- Kumar, K.; Kim, Y.-S.; Yang, E.-H. The Influence of Thermal Annealing to Remove Polymeric Residue on the Electronic Doping and Morphological Characteristics of Graphene. *Carbon* **2013**, *65*, 35–45.

- Woo, Y.; Duesberg, G. S.; Roth, S. Reduced Contact Resistance between an Individual Single-Walled Carbon Nanotube and a Metal Electrode by a Local Point Annealing. *Nanotechnology* **2007**, *18*, 095203–7.

- Jeong, O. L.; Park, C.; Ju-Jin, K.; Jinhee, K.; Jong Wan, P.; Kyung-Hwa, Y. Formation of Low-Resistance Ohmic Contacts between Carbon Nanotube and Metal Electrodes by

www.acsnano.org

a Rapid Thermal Annealing Method. J. Phys. D: Appl. Phys. 2000, 33, 1953–1956.

- Zhuravlev, L. T. The Surface Chemistry of Amorphous Silica. Zhuravlev Model. *Colloids Surf., A* 2000, 173, 1–38.

- Zhang, W.; Jie, J.; Luo, L.; Yuan, G.; He, Z.; Yao, Z.; Chen, Z.; Lee, C.-S.; Zhang, W.; Lee, S.-T. Hysteresis in In<sub>2</sub>O<sub>3</sub>:Zn Nanowire Field-Effect Transistor and Its Application as a Nonvolatile Memory Device. *Appl. Phys. Lett.* **2008**, *93*, 183111–3.

- Jin, S. H.; Islam, A. E.; Kim, T.-i.; Kim, J.-h.; Alam, M. A.; Rogers, J. A. Sources of Hysteresis in Carbon Nanotube Field-Effect Transistors and Their Elimination *Via* Methylsiloxane Encapsulants and Optimized Growth Procedures. *Adv. Funct. Mater.* **2012**, *22*, 2276–2284.

- 52. Wang, H.; Wu, Y.; Cong, C.; Shang, J.; Yu, T. Hysteresis of Electronic Transport in Graphene Transistors. *ACS Nano* **2010**, *4*, 7221–7228.

- Helbling, T.; Hierold, C.; Roman, C.; Durrer, L.; Mattmann, M.; Bright, V. M. Long Term Investigations of Carbon Nanotube Transistors Encapsulated by Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> for Sensor Applications. *Nanotechnology* 2009, 20, 434010–10.

- Won Lee, S.; Suh, D.; Young Lee, S.; Hee Lee, Y. Passivation Effect on Gate-Bias Stress Instability of Carbon Nanotube Thin Film Transistors. *Appl. Phys. Lett.* **2014**, *104*, 163506–4.

- Grigoras, K.; Zavodchikova, M. Y.; Nasibulin, A. G.; Kauppinen, E. I.; Ermolov, V.; Franssila, S. Atomic Layer Deposition of Aluminum Oxide Films for Carbon Nanotube Network Transistor Passivation. J. Nanosci. Nanotechnol. 2011, 11, 8818–8825.

- Liu, H.; Neal, A. T.; Si, M. W.; Du, Y. C.; Ye, P. D. The Effect of Dielectric Capping on Few-Layer Phosphorene Transistors: Tuning the Schottky Barrier Heights. *IEEE Electron Device Lett.* 2014, 35, 795–797.

- Saito, S.-i.; Torii, K.; Shimamoto, Y.; Tonomura, O.; Hisamoto, D.; Onai, T.; Hiratani, M.; Kimura, S. i.; Manabe, Y.; Caymax, M.; *et al.* Remote-Charge-Scattering Limited Mobility in Field-Effect Transistors with SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Gate Stacks. *J. Appl. Phys.* **2005**, *98*, 113706–9.

- Zeng, L.; Xin, Z.; Chen, S.; Du, G.; Kang, J.; Liu, X. Remote Phonon and Impurity Screening Effect of Substrate and Gate Dielectric on Electron Dynamics in Single Layer MoS<sub>2</sub>. *Appl. Phys. Lett.* **2013**, *103*, 113505–3.

- Shin, B.; Weber, J. R.; Long, R. D.; Hurley, P. K.; Walle, C. G. V. d.; McIntyre, P. C. Origin and Passivation of Fixed Charge in Atomic Layer Deposited Aluminum Oxide Gate Insulators on Chemically Treated InGaAs Substrates. *Appl. Phys. Lett.* 2010, *96*, 152908–3.

- Sharma, D.; Amani, M.; Motayed, A.; Shah, P. B.; Birdwell, A. G.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Dubey, M.; Li, Q.; et al. Electrical Transport and Low-Frequency Noise in Chemical Vapor Deposited Single-Layer MoS<sub>2</sub> Devices. Nanotechnology 2014, 25, 155702–7.

- Tsung-Hsien, K.; San-Lein, W.; Kai-Shiang, T.; Yean-Kuen, F.; Chien-Ming, L.; Chia-Wei, H.; Yi-Wen, C.; Osbert, C.; Shoou-Jinn, C. Trap Properties of High-k/Metal Gate pMOSFETs with Aluminum Ion Implantation by Random Telegraph Noise and 1/f Noise Measurements. *Jpn. J. Appl. Phys.* 2014, *53*, 04EC14–4.

- 62. Christensson, S.; Lundström, I.; Svensson, C. Low Frequency Noise in MOS Transistors—I Theory. *Solid-State Electron.* **1968**, *11*, 797–812.

- Rolland, A.; Richard, J.; Kleider, J. P.; Mencaraglia, D. Electrical Properties of Amorphous Silicon Transistors and MIS-Devices: Comparative Study of Top Nitride and Bottom Nitride Configurations. J. Electrochem. Soc. 1993, 140, 3679–3683.

- Knoch, J.; Zhang, M.; Appenzeller, J.; Mantl, S. Physics of Ultrathin-Body Silicon-on-Insulator Schottky-Barrier Field-Effect Transistors. *Appl. Phys. A: Mater. Sci. Process.* 2007, 87, 351–357.

- Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W. M. Reconfigurable Silicon Nanowire Transistors. *Nano Lett.* 2011, *12*, 119–124.

- Andres, C.-G.; Leonardo, V.; Elsa, P.; Joshua, O. I.; Narasimha-Acharya, K. L.; Sofya, I. B.; Dirk, J. G.; Michele, B.; Gary, A. S.;

Alvarez, J. V.; *et al.* Isolation and Characterization of Few-Layer Black Phosphorus. *2D Mater.* **2014**, *1*, 025001–19.

Joo, M.-K.; Kang, P.; Kim, Y.; Kim, G.-T.; Kim, S. A Dual Analyzer for Real-Time Impedance and Noise Spectroscopy of Nanoscale Devices. *Rev. Sci. Instrum.* **2011**, *82*, 034702–5.